中文核心期刊

# 光纤传感系统 SDRAM 控制器的 FPGA 设计与实现

王 宏¹ 张旭炜² 胡 挺² 王 刚² 李 焰² 苏一菲³

(1. 中国人民解放军 新疆军区指挥自动化工作站,乌鲁木齐 830001; 2. 中国电子科技集团公司 第三十四研究所,广西 桂林 541004; 3. 浙江工贸职业技术学院,浙江 温州 325000)

摘要:根据 SDRAM 的工作原理和接口时序特点 提出了一种基于 FPGA 的 SDRAM 控制器实现方法。采用 VHDL 在 MODELS IM 环境进行设计与仿真 较好地实现了各种工作状态的转换。在 Xi Linx 公司的器件上 利用 CHIPSCOPE 进行验证 实验结果表明 SDRAM 能够很好地完成读写操作。

关键词 SDRAM FPGA 设计

中图分类号·TN929.11 文献标识码:A 文章编号:1002-5561(2013)01-041-03

## Design and realization of the SDRAM controller based on FPGA used in fiber sensor system

WANG Hong<sup>1</sup>, ZHANG Xu-wei<sup>2</sup>, HU Ting<sup>2</sup>, WANG Gang<sup>2</sup>, LI Yan<sup>2</sup>, SU Yi-fei<sup>3</sup>

- (1. The Automation-Command Office of the Xinjiang Military Region. Orumqi 830001; 2. The 34th Institute of China Electronics and Technology Group Corporation, Guilin Guangxi 541004, China;

- 3. Zhejiang Industry & Trade Vocational College, Wenzhou Zhejiang 325000, China)

Abstract: Aimed at the working principle and the characteristics of time sequence, SDRAM controller implementation method was put forward based on FPGA. Design and emulator the program using the VHDL langue based on the model sim. The state machine in program runs well. The program is proved on xilinx device using the chipscope. The result indicates that FPGA can write and read data from SDRAM. Key words: SDRAM; FPGA; design

## 0引言

光纤传感系统中的信号处理单元作为高速数字 信号处理系统,需要使用 FPGA 来实现数据缓存。由于 FPGA内部的容量有限、限制了FPGA的使用、为了解 决这个问题,经常将大容量存储器外挂来实现数据缓 存。同步动态随机存储器(SDRAM)具有高速、大容量、 价格低廉和读写速度快等特点,并且在同一个 CPU 时 钟周期内即可完成数据的访问和刷新,其数据传输速 度远远大于传统的数据存储器(DRAM)。从而成为数据 缓存的首选存储介质、但 SDRAM 控制时序较复杂难 以实现,通常采用 FPGA 控制 SDRAM 有两种方法: ①采用开发环境自带的接口模块(比如 ISE 软件中自 带的 ipcore)。这种设计方法看起来比较简单,但通过 这种方法设计的程序通常透明度差、灵活度不高,这 就限制了这种方法的使用:②采用用户自编写的程序 来对 SDRAM 进行控制,这种方法看起来比较复杂,但 是比自带的接口模块使用更加灵活,通用性更强,移 植性比较好,特别适用于初学者。

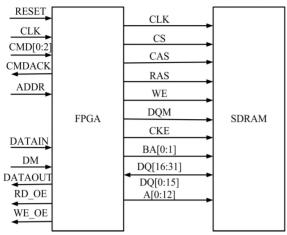

## 1 SDRAM 和 FPGA 的接口

本项目要存储的数据为 32bit 的整数, 因此采用 两片 MICRON 公司生产的 MT48LC16M16A2 为外部 存储器,它是一款 4Meg×16×4banks 存储器,由于单片 SDRAM 最大可以配置成 16bit 数据宽度,为了实现 32 位数据的存储,我们采用两块 SDRAM 进行位扩展。 SDRAM 与 FPGA 的接口示意图如图 1 所示。从图 1 可 以看出,FPGA和 SDRAM 之间的信号主要由地址信 号、数据信号和控制信号三大类组成。

①控制信号主要有:CLK (SDRAM 的时钟信号)、 CS(SDRAM 的片选信号)、CAS、RAS 和 WE(FPGA 对 SDRAM 读写控制命令), FPGA 通过这几个数据的组

收稿日期:2012-09-28。

作者简介:王宏(1957-),男,高级工程师,主要研究方向为边防电子信 息化建设和光电传感器。

#### 王宏,张旭炜,胡挺,等:光纤传感系统 SDRAM 控制器的 FPGA 设计与实现

图 1 FPGA 和 SDRAM 接口示意图

合来向 SDRAM 发出各种命令(读写数据、激活、刷新 等)、DOM(输入、输出控制命令)和 CKE(SDRAM 的时 钟使能信号)。

- ②地址信号有:BA0和BA1页地址选择信号(用 于选择 SDRAM 的不同页): A0~A12 地址信号. 这 13 条地址信号通过分时复用决定地址是行地址还是列 地址。

- ③数据信号有:由于采用两块 16bit 的 SDRAM 来 实现 32bit 数据的读写,数据总线的低 16bitDQ(0~15) 连接一块 SDRAM 数据线、数据总线的高位 DO (16~ 31)连接另外一块 SDRAM 的数据线。

#### 2 SDRAM 初始化操作

SDRAM 外部存储器上电后控制系统必须对它要 进行初始化操作,才能让 SDRAM 系统处于工作状态, 详细的初始化操作要经过以下几个步骤:

①系统上电并保持时钟稳定状态:②在系统时钟 稳定后要等待一段时间,等待时间应该大于100μs。在 待时间完成后至少执行一条指令禁止操作或者空操 作:③等待 TRP 个时钟周期,在这个时间必须执行空 操作命令,完成所有的块必须完成预充电,使所有的 块处于空闲状态: ④执行两个自动刷新 AUTO RE-FRESH 命令: ⑤保持几个周期的 NOP 命令后发出初 始化寄存器命令,完成对 SDRAM 工作模式的设定。

## 3 SDRAM 读写操作

FPGA 对 SDRAM 的写操作需要控制信号线和地 址线数据线配合才能完成。

- 3.1 FPGA 将数据写入 SDRAM 时所需步骤

- ①向 SDRAM 发出块激活命令、激活要写入数据 块同时锁存块的地址和行地址。

- ②在块激活命令后, 要等待 TRCD (本系统为 20ns)时间,通过控制线发出写命令,同时状态机跳转 到写状态并锁存列地址。

- ③写命令立即生效,需要写入的数据依次出现在 数据总线上。

- ④写入一个数据后. 延迟 tWR (1CLK+7.5ns)时 间 FPGA 向 SDRAM 发出预充电命令来关闭已激活的 页。

- ⑤等待 tRP(20ns)时间后,可进行下一次写操作。 FPGA 对 SDRAM 的读操作需要控制线和地址线数据 总线配合才能完成。

#### 3.2 FPGA 读出 SDRAM 中数据所需步骤

- ①向 SDRAM 发出块激活命令,并锁存相应的 BANK 地址和行地址。

- ②BANK 激活命令后, 等待 tRCD(20ns)时间, 通 过控制线发出读命令,同时状态机跳转到读状态并锁 存行列地址。

- ③延迟 CAS 个工作时钟后,要读出的数据会出现 在数据总线 DO 上。

- ④在读操作的最后、要向 SDRAM 发出预充电命 令,以关闭已经激活的页。

- ⑤等待 tRP 时间后,可以开始下一次的读。

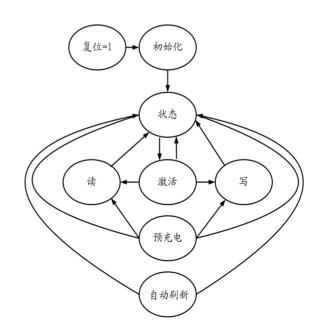

SDRAM 的读操作只支持突发模式(Burst Mode). 突发长度有1、2、4、8可选。本系统选择的突发长度为 8。详细的读写过程通过状态机来实现,状态机的状态 转换如图 2 所示。

图 2 FPGA 对 SDRAM 读写控制状态机

王宏,张旭炜,胡挺,等:光纤传感系统 SDRAM 控制器的 FPGA 设计与实现

#### 4 仿真结果

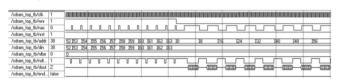

为了验证控制程序,我们在 modelsim 平台上对我 们编写的程序进行逻辑仿真。仿真条件:时钟为 50M: 复位信号高有效并持续两个时钟周期:写入的数据为 0~63 的自然数、读突发长度为 8。先将 64 个数写入 SDRAM 中、然后再将写入的数字在突发长度 8 的条 件下读出。仿真结果如图 3 所示。

从图 3 可以看出.我们在 50M 的时钟信号下将自 然数 0~63 连续写入 SDRAM 中, 然后在突发为 8 的条 件下,将这64个数分8次成功地读出,达到了预期的 效果。

图 3 逻辑仿真图

## 5 实验测试结果

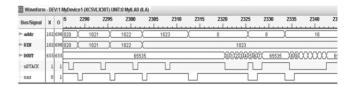

为了验证程序经过综合、映射和布局布线后的可 靠性,我们将程序下载到 FPGA 中,通过 CHIPSCOPE 将所需要的信号抓出分析。系统运行的条件是:时钟 为 100M, 复位信号高有效并持续三个时钟周期, 写入 的数据为 0~2047 的自然数,读突发长度为 8,FPGA 采 用 xilinx 公司的 VIRTEX5 系列中的 XC5VLX30T, SDRAM 采用 MICRON 公司 MT48LC16M16A2 两片进 行位扩展。CHIPSCOPE 抓图如图 4 所示。从图 4 可以

图 4 实际运行图

看出, 我们在 100M 的时钟下将 0~1023,1024 个数连 续写入 SDRAM 中、然后在突发为 8 的条件下将这 1024个数分128次成功地读出。达到了预期的效果。

#### 6 结束语

为了增加程序的可读性和灵活性,我们采用高级 编程语言 VHDL 通过自己编写的程序来实现对 SDRAM 存储器的读写操作,大大缩短了开发周期,同 时增加了程序的可读性和灵活性。采用逻辑仿真和将 程序下载到真实的系统中运行进行分析的方式来保 证程序的可靠性。都达到了预期的目的,该设计方法 具有一定的通用型,并已成功应用到光纤传感系统

#### 参考文献:

[1] 夏玉丽, 雷宏, 黄瑶.用 xilinx FPGA 实现 DDR SDRAM 控制器[J].微计 算机信息,2007,(23):210-211.

[2] MT48LC16M16A2 芯片资料[R].2002.

[3] 田丰,邓建国,李巍,等.SDRAM 控制器的设计与 VHDL 实现[J].电子 技术应用,2005,(2):74-77.

[4] Virtex5 FPGA User Guide 芯片资料[R].2007.

## 参考文献著录规则(二)——论文集、专利文献、学位论文和科技报告的著录格式

#### ◆论文集的著录格式.

[序号] 著者. 题名[C]//著者.专题名:其他题名.出版地:出版者,出版年:起-止页码.

[1] 白书龙. 植物开花研究[C]//李承森. 植物科学进展.北京:高等教育出版社,1998:146-163.

#### ◆专利文献著录格式:

[序号] 专利申请者或所有者. 专利名称:专利国别,专利号[文献类型标志]. 公告日期或公开日期[引用日 期1. 获取和访问路径.

## ◆学位论文著录格式

[序号] 作者.题名[文献类型标志].保存地:保存者,年份.

[1] 李洁.促进我国国家创新系统中知识流动的政策分析[D].北京:中国科学院文献情报中心,2004.

## ◆科技报告的著录格式:

[序号] 主要责任者. 题名:其他题名信息[文献类型标志]. 其他责任者. 版本项. 出版地:出版者,出版年: 起-止页码.

[1] World Health Organization. Factor regulating the immune response; report of WHO Scientific Group[R].